### Quick Start for Advanced Design System (ADS) in Power Electronics Applications

Colin Warwick

Product Owner for Power Electronics Keysight EEsof EDA

7/31/2015

### Evaluate ADS for design of power electronics

New devices (SiC, GaN) and their fast edges require new thinking about EDA tools

- Need Harmonic Balance: Yields steady state solution rapidly

- Three reasons to apply an EM field solver to your "virtual prototype":

- PCB traces and vias add significant parasitic impedances to your circuit

- 2. Create EM-based models of integrated magnetics

- 3. Model EMI/EMC

Traditional SPICE falls short...

| SPICE                  | Time domain | Frequency domain |

|------------------------|-------------|------------------|

| Lumped components      | Yes         | No               |

| Distributed components | No          | No               |

#### ...but ADS can tackle the issues:

| ADS                    | Time domain | Frequency domain |

|------------------------|-------------|------------------|

| Lumped components      | Yes         | Yes              |

| Distributed components | Yes         | Yes              |

#### How to Evaluate ADS

Overview: Three steps

- 1. Download and install the binaries

- 2. Request a no-charge 45-day evaluation license

- 3. Follow the click-by-click demonstration in this Quick Start guide

### Step One

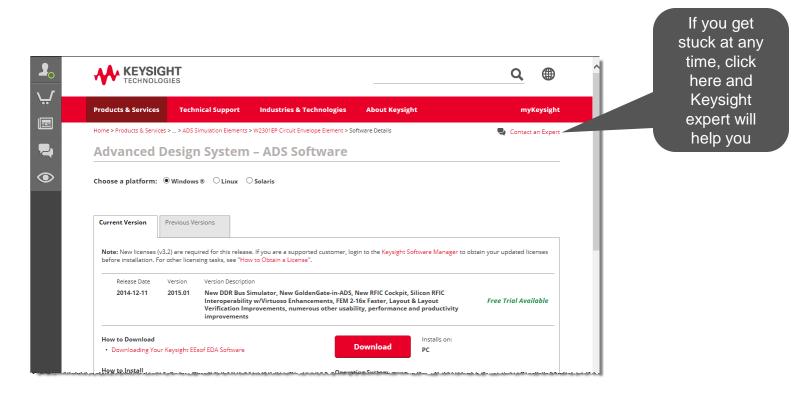

#### Download and install the binaries

http://www.keysight.com/find/eesof-ads-latest-downloads

### Step Two

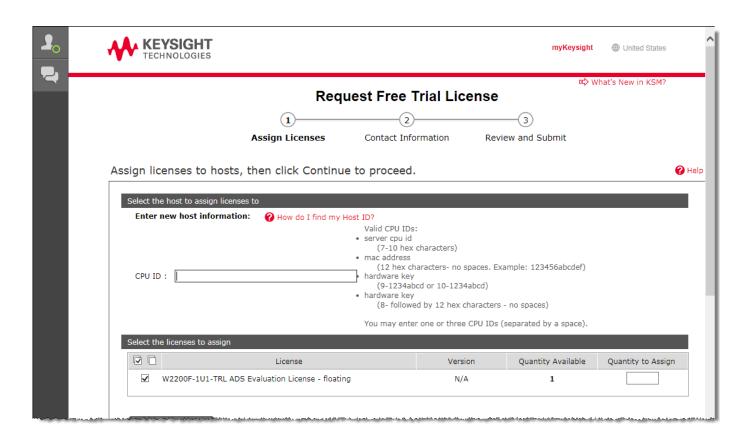

#### Request a no-charge 45-day evaluation license

http://www.keysight.com/find/eesof-ads-evaluation

### Step Three

#### Follow this hands-on demonstration

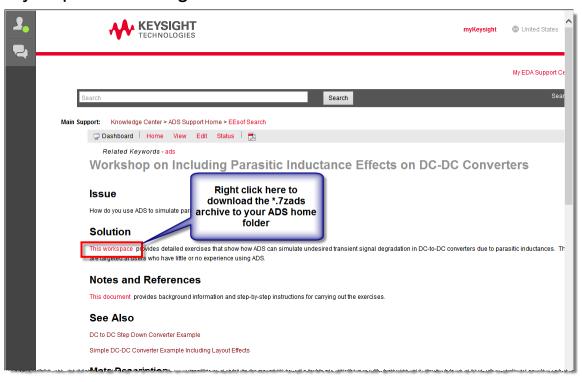

- Go to:

- http://edadocs.software.keysight.com/display/eesofkcads/Workshop+on+Including+Parasitic+Inductance+Effects+on+DC-DC+Converters

- ..and download the archived ADS workspace (as shown below) to the "home folder" that you picked during ADS installation:

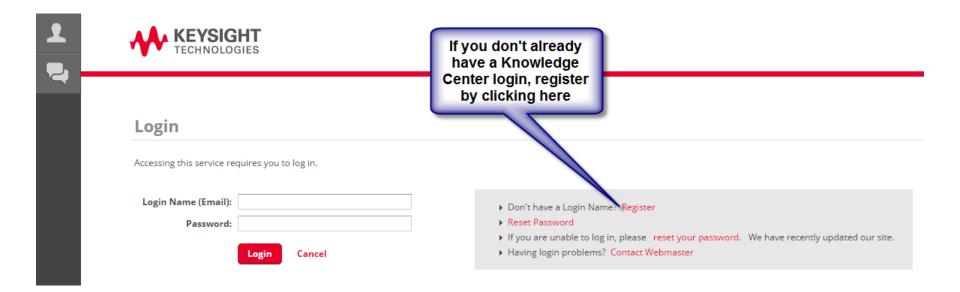

# Note: If you didn't receive a Knowledge Center login with the demo license, please register now

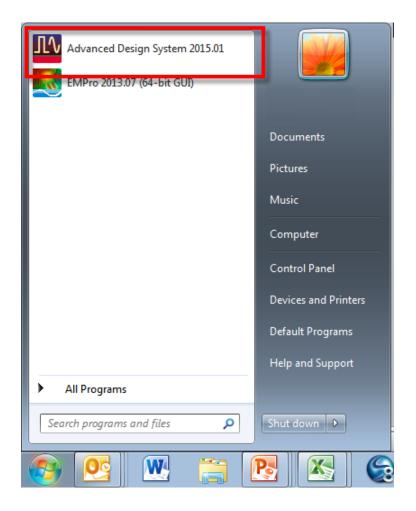

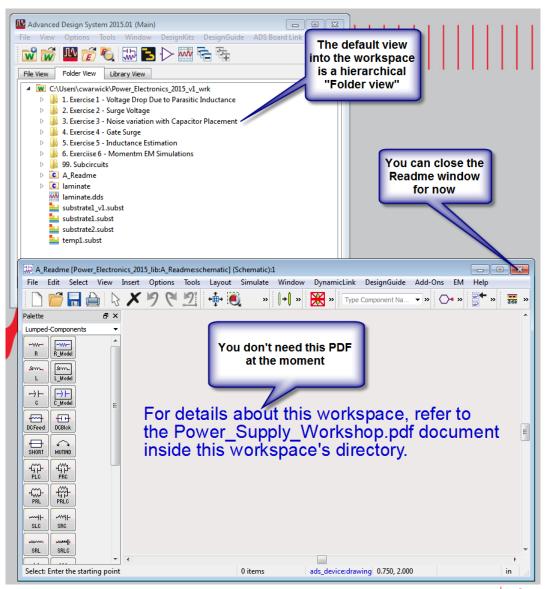

### Start Advanced Design System

Start → Advanced Design System

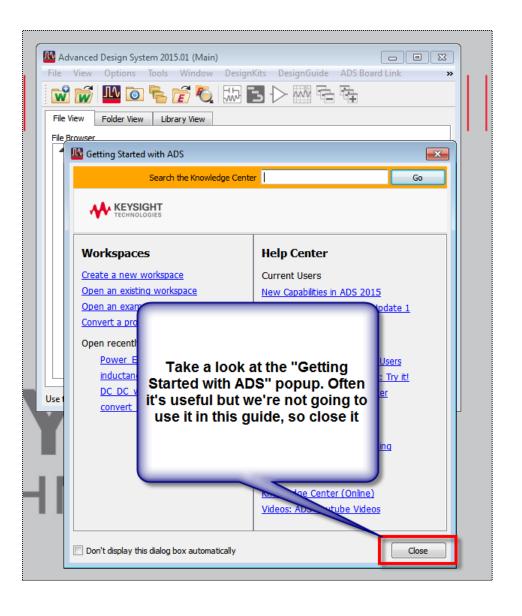

### Two windows open...

- ...examine but then close the "Getting Started with ADS" popup window

#### The ADS "Main" window remains...

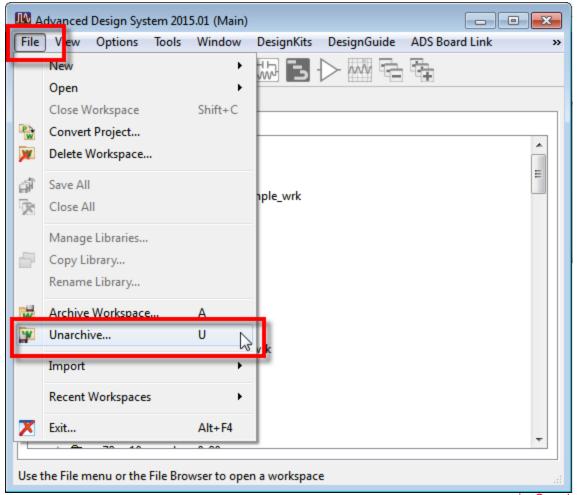

From the Main window menu bar, select the File

Unarchive... dialog box

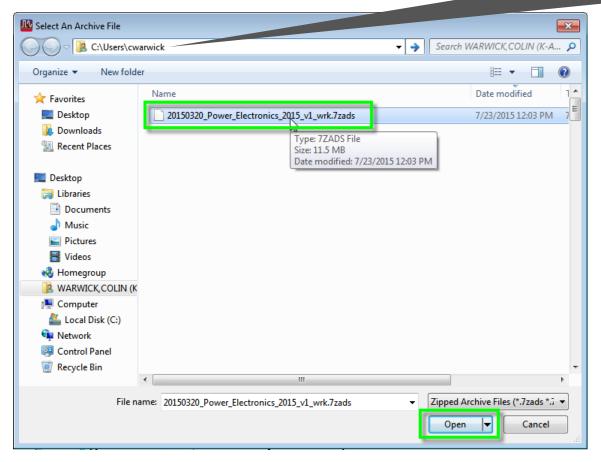

Select and open the \*.7zads archive you

downloaded

I downloaded the archive to C:\Users\cwarwick. Of course, you'll need to navigate to the folder you picked.

This guide doesn't cover the principles of operation but our YouTube video "How to Design DC-DC Convertors" has a refresher if you need one.

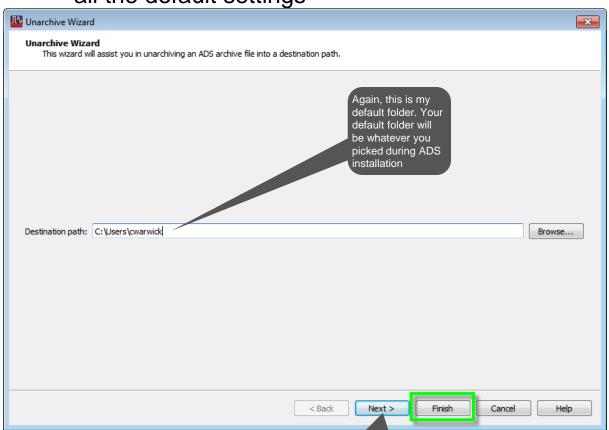

### Accept the default settings of the Unarchive Wizard

Ignore the "Next" button and just click the "Finish" button to accept all the default settings

### Close the Readme window, leaving "Main" open

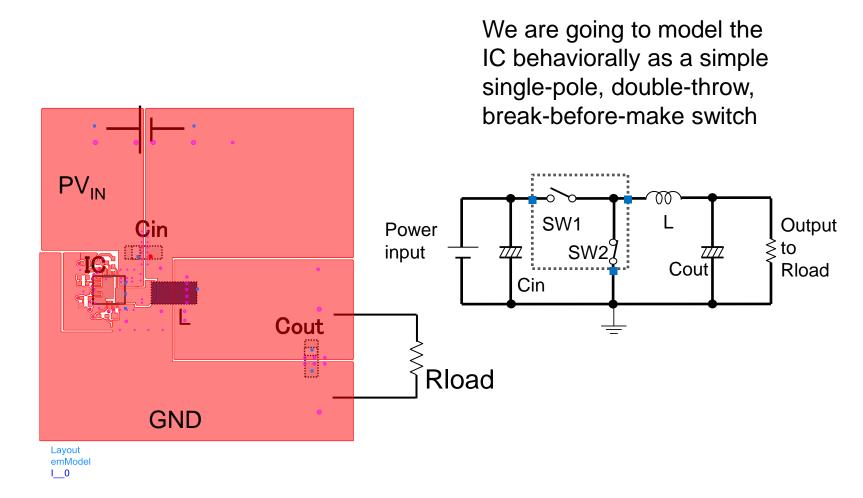

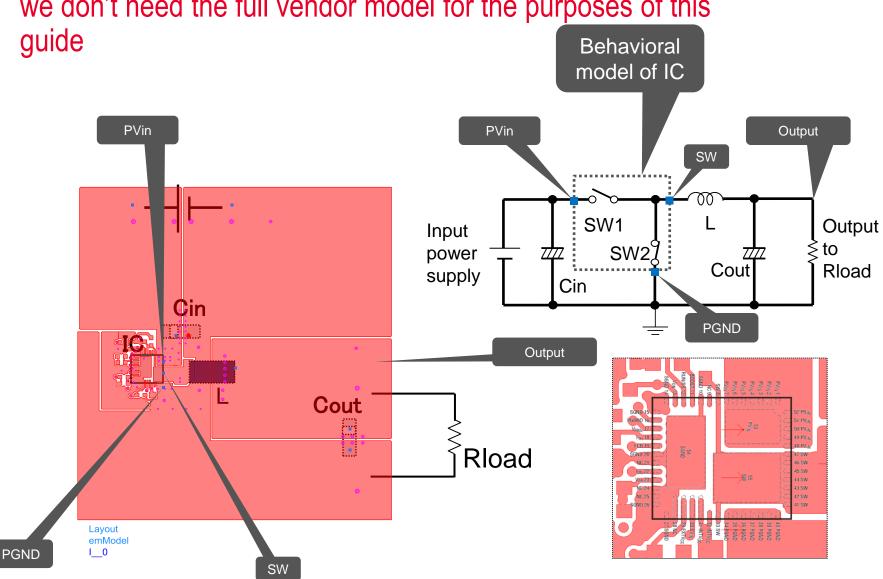

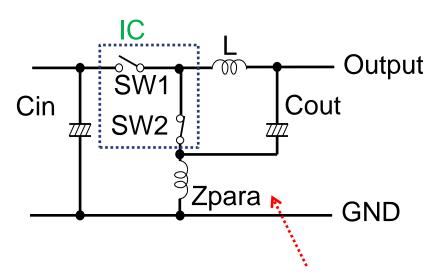

# We are going to model a switch-mode DC-DC convertor. Here's a simplified version...

Side note: The actual IC is LTC3609 from Linear Technology, but we don't need the full vendor model for the purposes of this

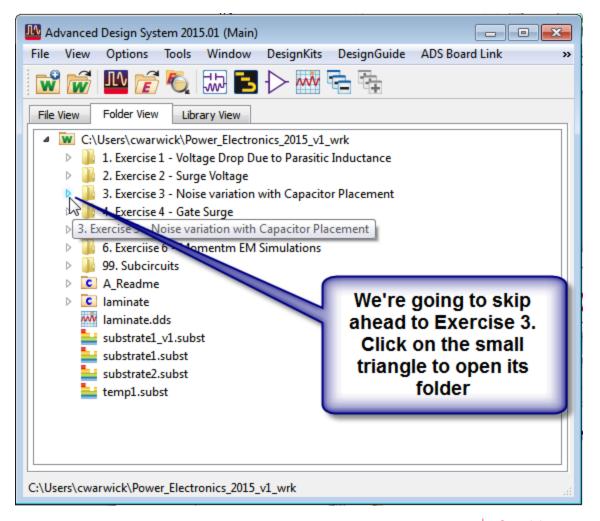

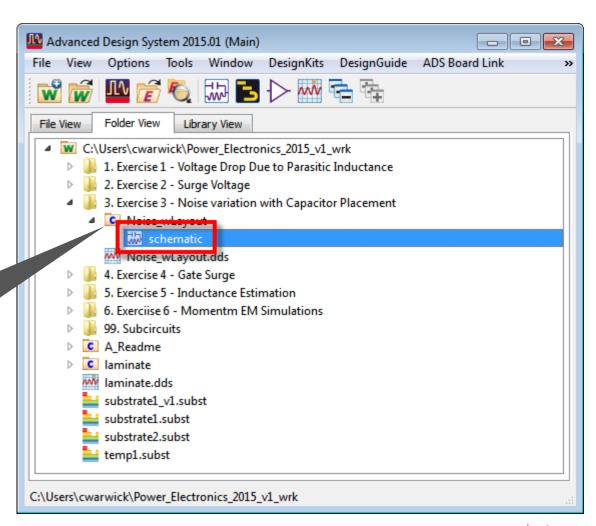

### Let's see the real thing: Open the Exercise 3 folder

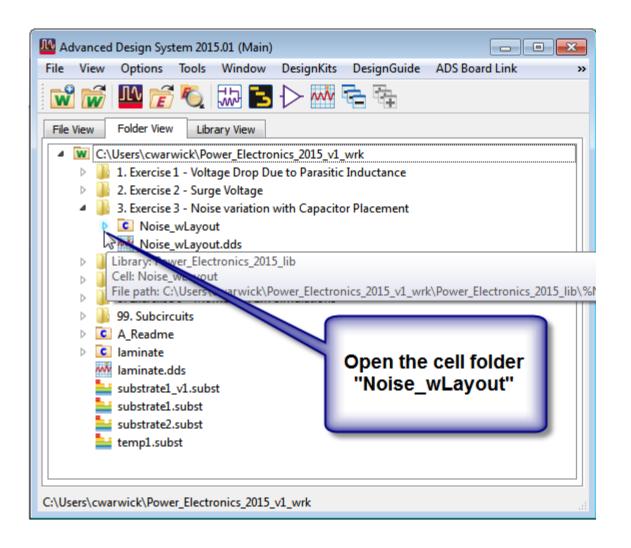

### Open the cell folder "Noise\_wLayout

### Side note: Multi-technology in ADS

#### Skip this slide if you like and come back to the idea later

- A Workspace contains one or more Technology Libraries

- Q. Why would you want multiple technologies? A. For example, chip, package, and board can have their own Technology Library, each with their own namespace, stack up, component library, PDK, etc.

- A Technology Library contains one or more design units (subcircuits), called "Cells"

- Q. Why would you want more than one? A. You might want hierarchy e.g. subcircuit cells instantiated on a top-level circuit cell. You can even instantiate a cell from one tech. library inside of a cell from another. For example, to place a chip in a package, and a package onto a PCB, just like the real world.

- A Cell can be viewed in one or more ways, called "Views"

- Q. What are the names of some Views? A. The "black box" view is called "Symbol view", the circuit view is "Schematic", the flat physical view is "Layout view", the perspective physical view is called "3D layout view" and so on

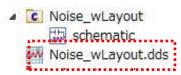

# Double click on "schematic" view of the Noise\_wLayout cell

Folders that contain Cells and Views of the Cell have a letter "C" on them

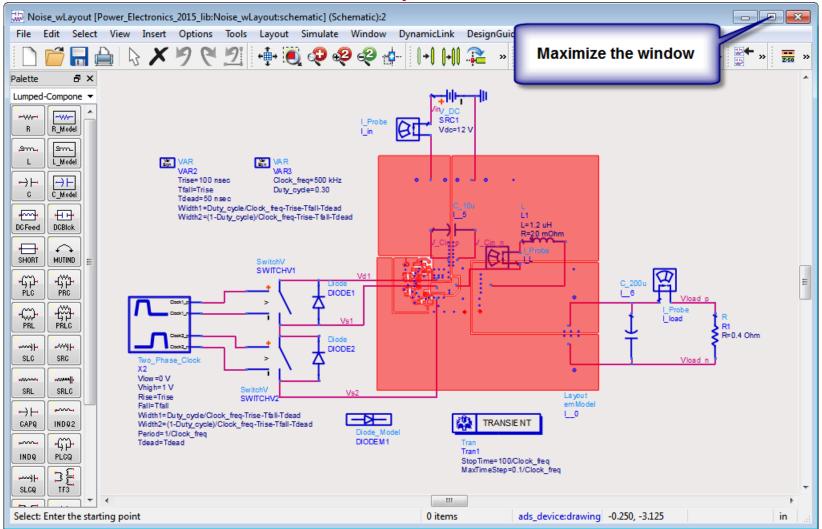

# There is a lot going on here, so maximize the window, and let's take a quick tour...

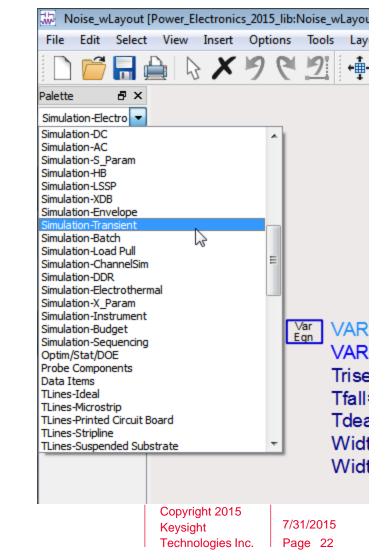

### The top-level schematic has a simulation controller

- In this particular case we are using the time-domain SPICE-like simulator in ADS called "Transient"

- It includes a Convolution engine so it is sometimes called "Transient Convolution" or just "TC"

TRANSIENT

Tran

Tran1

StopTime=100/Clock\_freq

MaxTimeStep=0.1/Clock\_freq

**Note**: Transient is just one of many circuit simulators available for ADS...

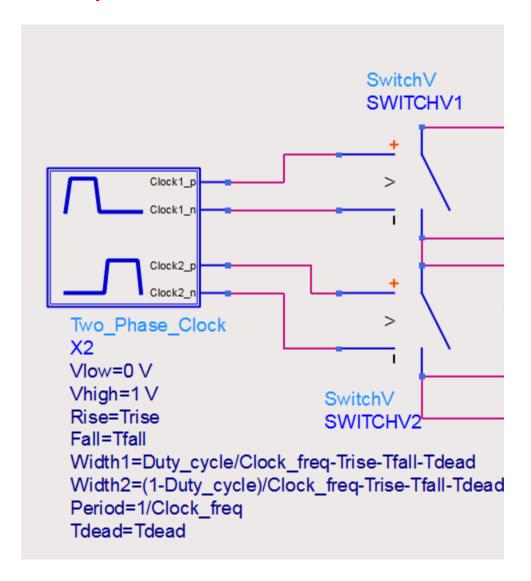

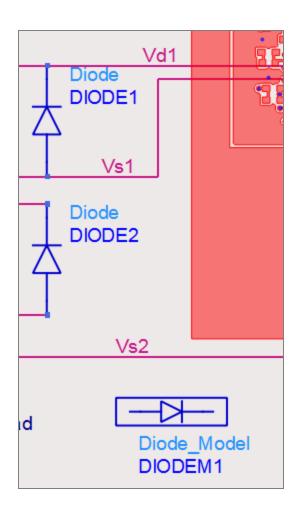

### Components can be modelled behaviorally...

In this guide we model the IC as an ideal single-pole, double throw, break-before-make switch

#### ...or using physics-based, vendor-specific "model cards"

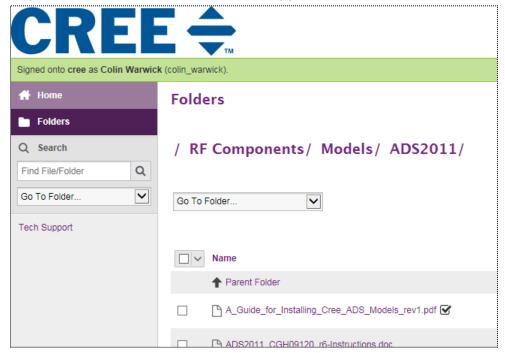

Note: Not used in this guide, but many microelectronic vendors offer models for ADS. For example, Cree:

http://www.cree.com/RF/Tools-and-Support/Model-form

### VAR blocks contain expressions evaluated before the simulation runs

Can be convenient for parameterization, especially for parameter sweeps

```

Var VAR

VAR2

VAR3

Trise=100 nsec

Clock_freq=500 kHz

Tfall=Trise

Duty_cycle=0.30

Tdead=50 nsec

Width1=Duty_cycle/Clock_freq-Trise-Tfall-Tdead

Width2=(1-Duty_cycle)/Clock_freq-Trise-Tfall-Tdead

```

Note: ADS also has EQN or Measurement Equation blocks, which are similar to VAR blocks, but contain expressions that are evaluated *after* the simulation has run. Useful for analysis of simulation results, waveforms etc.

### Most important: the "Look-alike" component

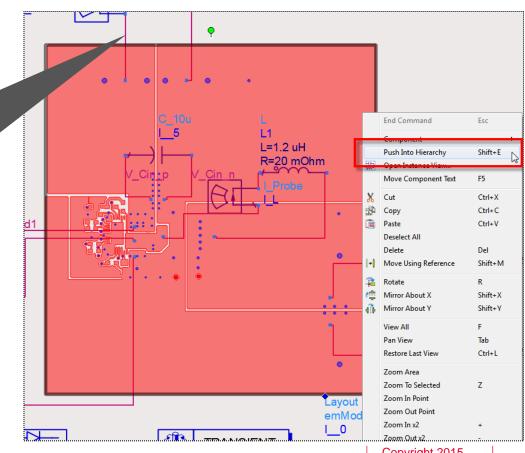

The EM field solver in ADS can extract a model of the layout parasitics! Right click on it and select "Push into Hierarchy" from its popup context menu

Note: The connection between the lumped component and the distributed component is represented by a magenta line with a blue square at each end

Copyright 2015 Keysight Technologies Inc.

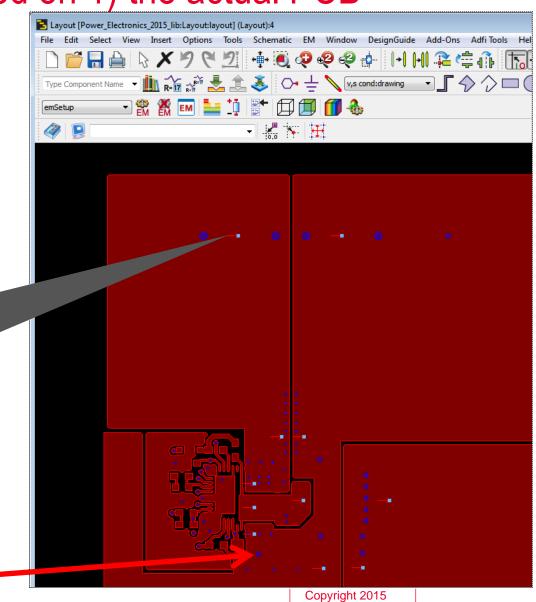

## Under the hood are details of the EM model. Click on the layout icon to open the artwork

Opens the layout view of the cell called "Layout"

The EM model is based on 1) the actual PCB

artwork...

Note: In layout

view, a "pin" is

represented by

small cyan

square with a red

arrow coming out

The dark blue circles are via holes

Keysight

Technologies Inc.

7/31/2015

Page 28

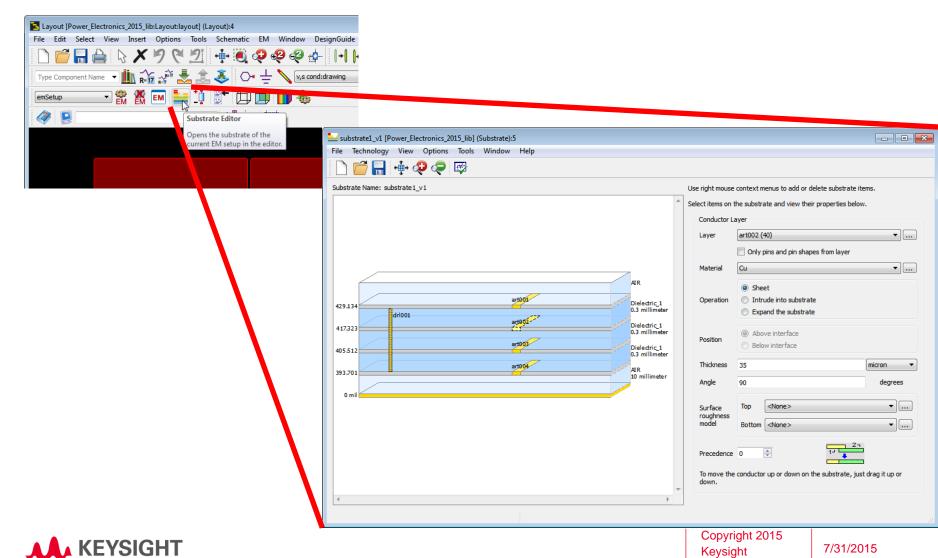

# ...and 2) the material properties of the stackup of the technology library that the layout is in

Technologies Inc.

Page 29

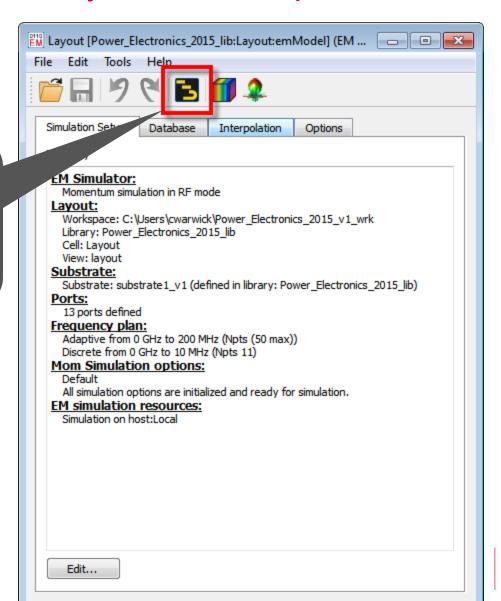

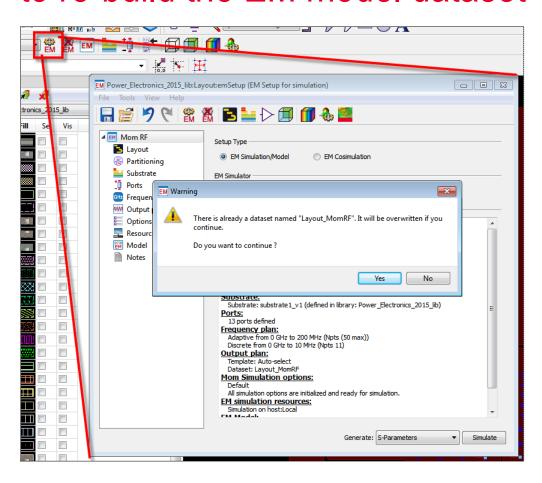

### Optional: Click the EM cog icon, and click "Yes" to re-build the EM model dataset

Caution: If you perform this optional step, the EM simulation takes about 20 minutes on a typical PC. This step is optional because we already ran the EM simulation for you and saved the resulting dataset in your workspace.

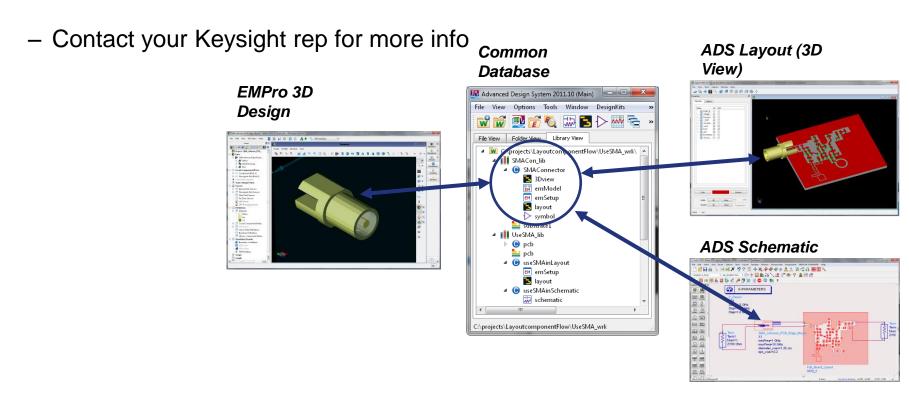

# Side note: The EMPro add-on to ADS can build EM models of arbitrary 3D shapes like magnetics and integrate them with layout and schematic

Advanced topic: not covered further in this guide

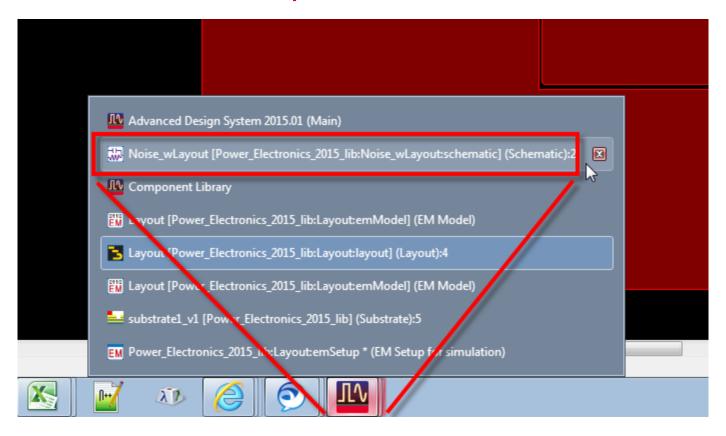

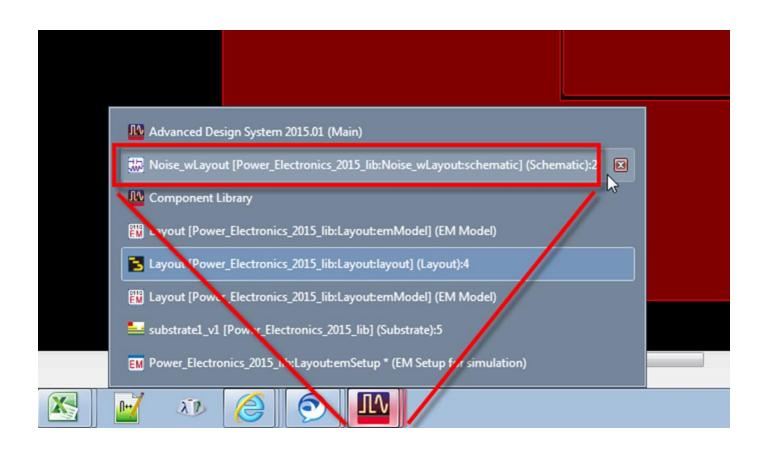

## From the Windows task bar, bring the original schematic back on top

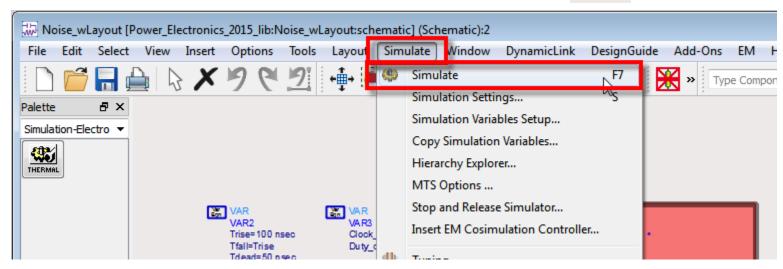

### From the schematic menu bar, select Simulate Simulate

**Note:** You could also:

1) Use the F7 hotkey or

2) Click the simulate (cog wheel) icon in the tool bar:

After a few seconds, the simulation finishes, and the data display window opens automatically...

Side note: The \*.dds file extension means "data display server"

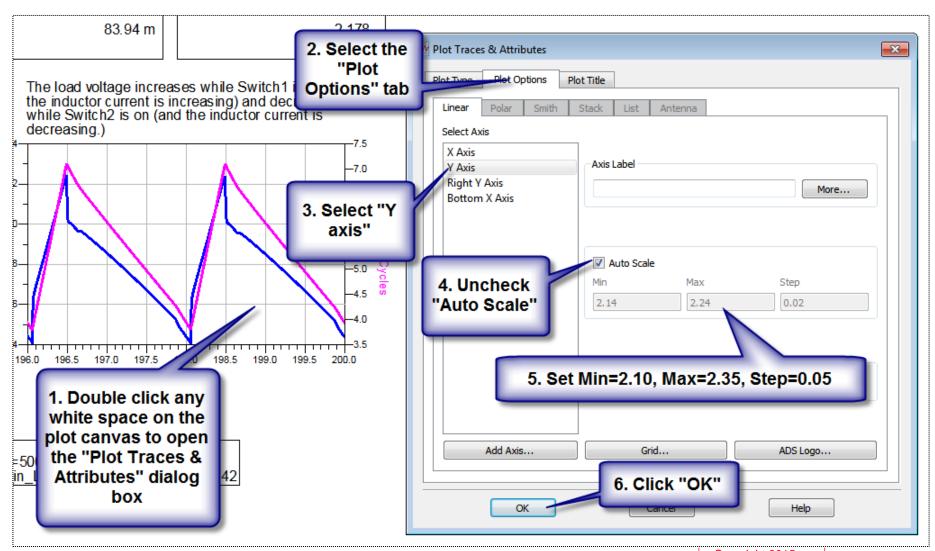

### Rescale the Y-axis in the baseline ripple plot

...in preparation for comparing this "good" design with the "bad" one that we'll do next

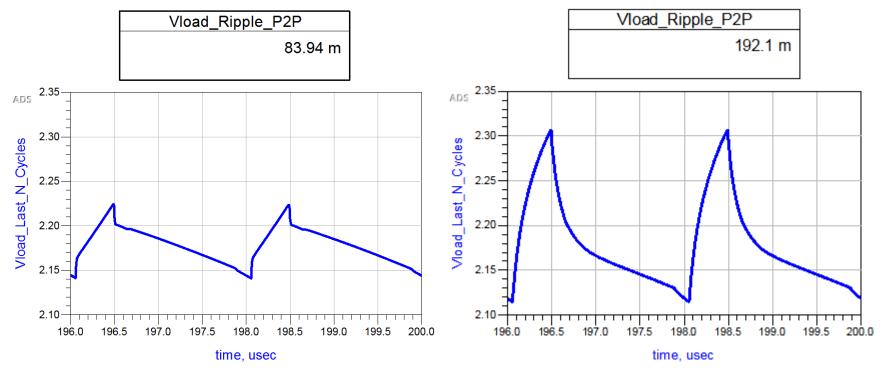

#### Next let's see the effect of layout parasitics on ripple...

Parasitic impedance causes more ripple noise

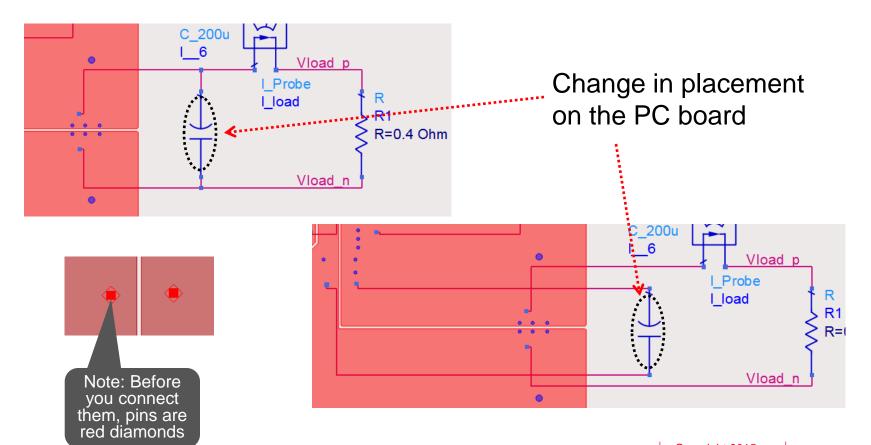

Let's show what happens to ripple if we add a parasitic impedance by artificially increasing the trace length between Cout and the output ports to Rload

### Bring the schematic window back on top

# We are going to change the connection points of C\_200u (Cout)

Exact steps are on the next slide...

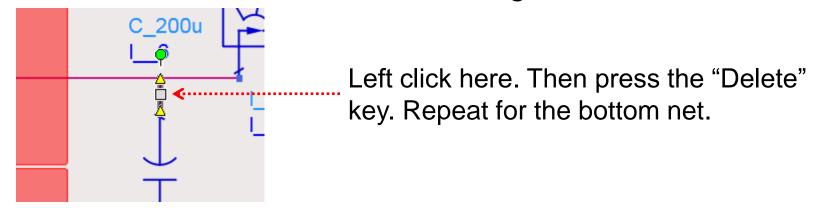

### How to change the connection points

1. Left click to select the wire. Next, hit the Delete key. Remove the other wire connecting C\_200u.

2. After clicking \int \, left click on the nodes as shown to re-connect the capacitor.

New port connections

R=I

Vload p

Vload n

I Probe I load

### Re-run with "bad" connection points

Click to re-run the simulation. The "display dataset" window comes into focus again.

Before: Low layout parasitic

After: High layout parasitic

Note: Do Y-axis scaling on the new plot as before

#### Conclusion and Next Steps

In power electronics, ADS can solve problems that

Time domain

SPICE alone cannot

This guide has just a small taste! Contact your Keysight EEsof EDA expert for further e-learning material to meet your needs! http://www.keysight.com/find/eesof-support

Frequency domain

| 002                    | Tillio dollialii | 1 requeries aermani |  |  |

|------------------------|------------------|---------------------|--|--|

| Lumped components      | Yes              | No                  |  |  |

| Distributed components | No               | No                  |  |  |

|                        |                  |                     |  |  |

| ADS                    | Time domain      | Frequency domain    |  |  |

| Lumped components      | Yes              | Yes                 |  |  |

| Distributed components | Yes              | Yes                 |  |  |

SPICE